pcb设计中常见的走线等长要求是什么

线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的 PCB 信号等长处理。等长的目标是为了满足同组信号的时序匹配要求。

2、等长范围应严格遵守不同接口或者信号的要求,具体的可参考模块规范内容。如若有疑问,及时与客户进行确认。

3、处理等长之前应先把同组内线长最长的信号线找到,第一步优化最长信号的长度。

4、等长处理完后应对整根信号线路径进行检查,检查其是否避开干扰源,检查其是否合格。

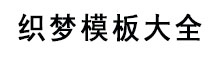

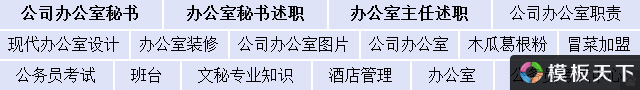

5、等长处理时,间距优选4W,如空间受限,可调整到3W;等长高度控制在40-150mil为宜,不能过高;转角长度不小于线mil大小,如线mil,转角大小控制在6mil,转角不能太小,如图1所示。

图1 蛇形走线、等长应尽量处理在水平或竖直方向上,避免处理在斜线上;处理不能太过散乱,应尽量集中处理,保证其美观性,原则上是处理完一根信号后,第二根先修线挨到其旁边,再对第二根进行等长处理,以保证空间的利用率及整体设计美观性。同一设计内,等长的高度应控制差不多相同,不要相差太多,如图2。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。天选团队文章及其配图仅供工程师学习之用,如有内容图片侵权或者其他问题,请联系本站作侵删。侵权投诉

线ps/inch,再根据芯片运行速度和信号上升时间保持时间,推算出具体

数据信号组:以地平面为参考,给信号回路提供完整的地平面。特征阻抗控制在50~60 Ω。线宽

的方向等有什么关系?需要注意哪些设计指标来避免出现串扰等问题? 答:串扰会影响边沿速率,一般来说,一组总线传输方向相同时,天选串扰因素会使边沿速率变慢

开窗 /

主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高

主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

的重要事项 /

的错误有哪些? /

西门子plc S7-1200/S7-1500优化的DB块与标准的DB块整体对比

相关文章:

相关推荐:

网友评论: